CH7520

- If you have questions about the product, or encounter any, you can register the site account,

- Then go to the technical support forum to ask for help.

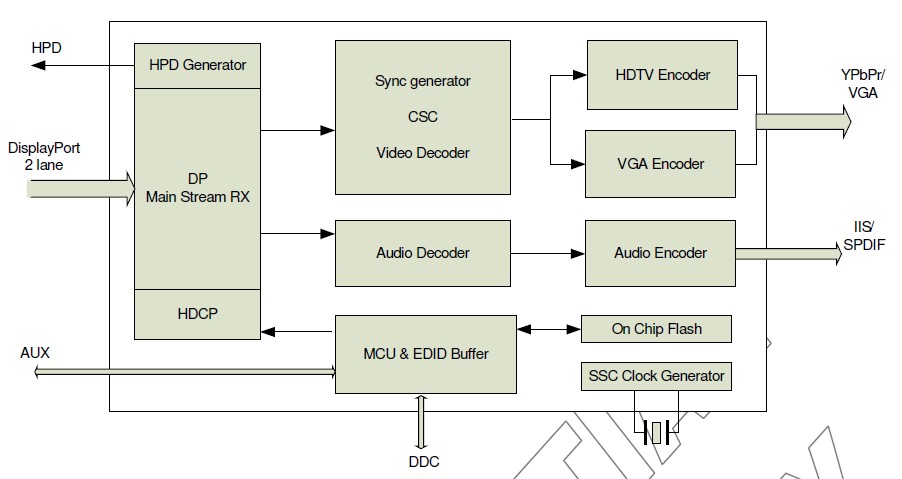

Chrontel’s CH7520 is a low-cost, low-power semiconductor device that translates the DisplayPort signal to the VGA or YPbPr. This innovative DisplayPort receiver with integrated HDTV encoder and three separate 9-bit video Digital-to-Analog Converters (DACs) is specially designed to target the DisplayPort Docking Station, Automobile Entertainment Device, Notebook/Ultrabook and PC market segments. Through the CH7520’s advanced decoding / encoding algorithm, the input DisplayPort high-speed serialized multimedia data can be seamlessly converted to analog RGB or HDTV video and IIS or SPDIF audio output.

The CH7520 is compliant with the DisplayPort Specification 1.2. With internal HDCP key Integrated, the device support HDCP 1.3 specifications. In the device’s receiver block, which supports two DisplayPort Main Link Lanes input with data rate running at either 1.62Gb/s or 2.7Gb/s, can accept RGB digital formats in either 18- bit 6:6:6 or 24-bit 8:8:8, and converted the input signal to VGA and YPbPr. Leveraging the DisplayPort’s unique source/sink “Link Training” routine, the CH7520 is capable of instantly bring up the video display to the analog HDTV and VGA monitor when the initialization process is completed between CH7520 and the graphic chip.

The DACs are based on current source architecture. And the VGA output meet VESA VSIS v1r2 clock jitter target. With sophisticated MCU and the Boot ROM embedded, CH7520 supports auto-boot and EDID buffer. After the configuration by firmware, which is auto loaded from Boot ROM, CH7520 can support DP input detection, TV/VGA connection detection and determine to enter into Power saving mode automatically.

Chrontel’s CH7520 is a low-cost, low-power semiconductor device that translates the DisplayPort signal to the VGA or YPbPr. This innovative DisplayPort receiver with integrated HDTV encoder and three separate 9-bit video Digital-to-Analog Converters (DACs) is specially designed to target the DisplayPort Docking Station, Automobile Entertainment Device, Notebook/Ultrabook and PC market segments. Through the CH7520’s advanced decoding / encoding algorithm, the input DisplayPort high-speed serialized multimedia data can be seamlessly converted to analog RGB or HDTV video and IIS or SPDIF audio output.

The CH7520 is compliant with the DisplayPort Specification 1.2. With internal HDCP key Integrated, the device support HDCP 1.3 specifications. In the device’s receiver block, which supports two DisplayPort Main Link Lanes input with data rate running at either 1.62Gb/s or 2.7Gb/s, can accept RGB digital formats in either 18- bit 6:6:6 or 24-bit 8:8:8, and converted the input signal to VGA and YPbPr. Leveraging the DisplayPort’s unique source/sink “Link Training” routine, the CH7520 is capable of instantly bring up the video display to the analog HDTV and VGA monitor when the initialization process is completed between CH7520 and the graphic chip.

The DACs are based on current source architecture. And the VGA output meet VESA VSIS v1r2 clock jitter target. With sophisticated MCU and the Boot ROM embedded, CH7520 supports auto-boot and EDID buffer. After the configuration by firmware, which is auto loaded from Boot ROM, CH7520 can support DP input detection, TV/VGA connection detection and determine to enter into Power saving mode automatically.

Input Interface eDP/DP

Output Interface VGA, YPbPr

Audio Interface IIS, SPDIF Output

Other features No

Package Type QFN40

Part Number Package Type Operating Temperature Range Minimum Order Quantity

CH7520A-BF 40 QFN, Lead-free Commercial : -20 to 70°C 490/Tray

CH7520A-BFI 40 QFN, Lead-free Industrial : -40 to 85°C 490/Tray

Copyright © 1998-2017 Chrontel, Inc. All Rights Reserved. Privacy protection Legal statement