CH7018

- If you have questions about the product, or encounter any, you can register the site account,

- Then go to the technical support forum to ask for help.

TV-Out:

LVDS-Out:

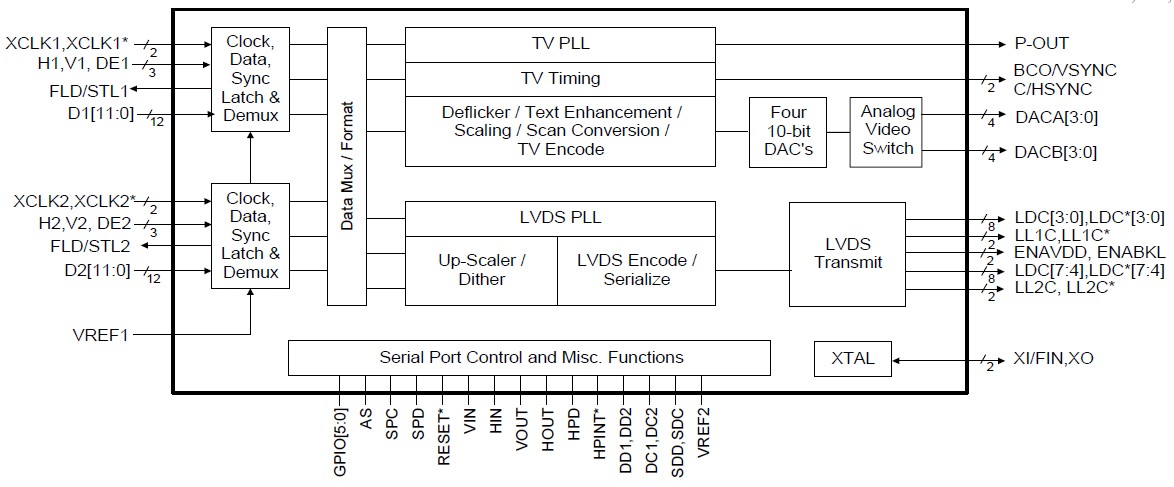

The CH7018 is a Display Controller device that accepts two digital graphics input data streams. One data stream outputs through an LVDS transmitter to a LCD panel, while the other data stream is encoded for NTSC or PAL TV and outputs through four 10-bit high-speed DACs. The TV encoder device encodes a graphics signal up to 1024x768 resolution and outputs the video signals according to NTSC or PAL standards. The LVDS transmitter operates at pixel speeds up to 165MHz per link, supporting 1600x1200 panels at 60Hz refresh rate.

The device can also accept one graphics data stream over two 12-bit wide variable voltage ports which support nine different data formats including RGB and YCrCb (RGB must be used for LVDS output). A maximum of 330M pixels per second can be output through dual LVDS links.

The TV-Out processor will perform non-interlaced to interlaced conversion with scaling, flicker filtering, and encoding into any of the NTSC or PAL video standards. The scaler and flicker filter are adaptive and programmable for superior text display. Eight graphics resolutions are supported up to 1024 by 768 pixels with full vertical and horizontal under-scan capability in all modes. A high accuracy low jitter phase locked loop is integrated to create outstanding video quality. In addition to TV encoder modes, bypass modes are included which allow the TV DACs to be used as a second CRT DAC.

The LVDS transmitter includes a panel fitting up-scaler and a programmable dither function for the support of 18-bit panels. Data is encoded into commonly used formats, including those detailed in the OpenLDI and the SPWG specifications. Serialized data outputs on three to eight differential channels.

Input Interface DVO , TTL/Digital RG

BOutput Interface LVDS, VGA, CVBS , S-Video, YPbPr

Audio Interface No

Other features Scaler, Line Buffer

Package TypeLQFP128

Copyright © 1998-2017 Chrontel, Inc. All Rights Reserved. Privacy protection Legal statement